# SiC レクチャーシリーズ

10. SiC プロセス技術 (2) ゲート絶縁膜

## SiC プロセス技術 (2) ゲート絶縁膜

SiC は Si と同様の熱酸化プロセスにより良質な  $\text{SiO}_2$  絶縁膜をウェハの表面に形成できます。このことは SiC デバイスの作製において非常に大きなメリットとなっています。プレーナ型 SiC MOSFET では、通常、この熱酸化  $\text{SiO}_2$  をゲート絶縁膜として利用して製品化がなされています。しかしながら、SiC の熱酸化に関しては Si とは異なる点もいくつか存在するため、それらを考慮しながら SiC デバイスプロセスへの熱酸化の適用を進めなければいけません。

まず SiC の熱酸化は Si と比較し酸化速度が小さいです。このため、プロセスには長時間がかかり、また、高温を必要とします。SiC の熱酸化では高温プロセスによる装置への負荷の配慮が不可欠となります。また、SiC の熱酸化速度は結晶面に依存した大きな異方性をもっています。熱酸化速度は、通常、デバイスが作製される(0001)Si 面で最も遅く、(000-1)C 面で最も速いです。例えばトレンチ型 SiC MOSFET を作製する際は Si 面、C 面と直交する面にゲート酸化膜を形成するため、CVD 酸化膜を利用するなどの対策が必要となります。熱酸化の雰囲気については水蒸気雰囲気とドライ酸素雰囲気が用いられており、両者を比較した場合、Si と同様に水蒸気雰囲気の方が酸化速度は大きいです。後述する SiC/ $\text{SiO}_2$  界面の電子、正孔トラップの形成に雰囲気ガスが影響するため、雰囲気ガスの選択には注意を要します。なお、SiC を構成する炭素については熱酸化において CO あるいは  $\text{CO}_2$  の形で  $\text{SiO}_2$  から脱離します。SiC の熱酸化により形成された  $\text{SiO}_2$  は、SiC/ $\text{SiO}_2$  界面の近傍を除いて、炭素の残留は非常に少ないことが分かっています。SiC に対し、適切な条件で形成した熱酸化  $\text{SiO}_2$  の絶縁破壊電界強度は Si の熱酸化による  $\text{SiO}_2$  の値と比較し、同程度かそれ以上の良好な値が得られており、電気的な絶縁性能に関する本質的な問題はありません。

SiC と Si の熱酸化膜で大きく異なる点として、SiC では SiC/ $\text{SiO}_2$  界面に多くの電子、正孔トラップが形成されることが挙げられます。SiC/  $\text{SiO}_2$  界面におけるトラップは MOSFET のオン時の抵抗を増加させ、特性に経時変化を生じさせるなどのデバイスの性能に悪影響を与えます。このため、界面トラップの密度を低減する試みが多くなされています。これらのうち NO や  $\text{N}_2\text{O}$  などの窒化処理ガス雰囲気において SiC/ $\text{SiO}_2$  界面のアニール処理を行うことは、既に広く用いられている手法であり、MOSFET の SiC/ $\text{SiO}_2$  界面における電子の実効移動度を大きく改善できます。この窒化アニール処理を行う際の温度は熱酸化プロセスと同程度の温度もしくはさらに高い温度が必要で、高温に対応したアニールプロセス装置が必要です。電子、正孔トラップの起源については、残留炭素が関与した複合欠陥などが考えられていますが、未だ議論が続いている。また、トラップ密度をさらに低減するための研究開発多くの機関で継続して進められています。

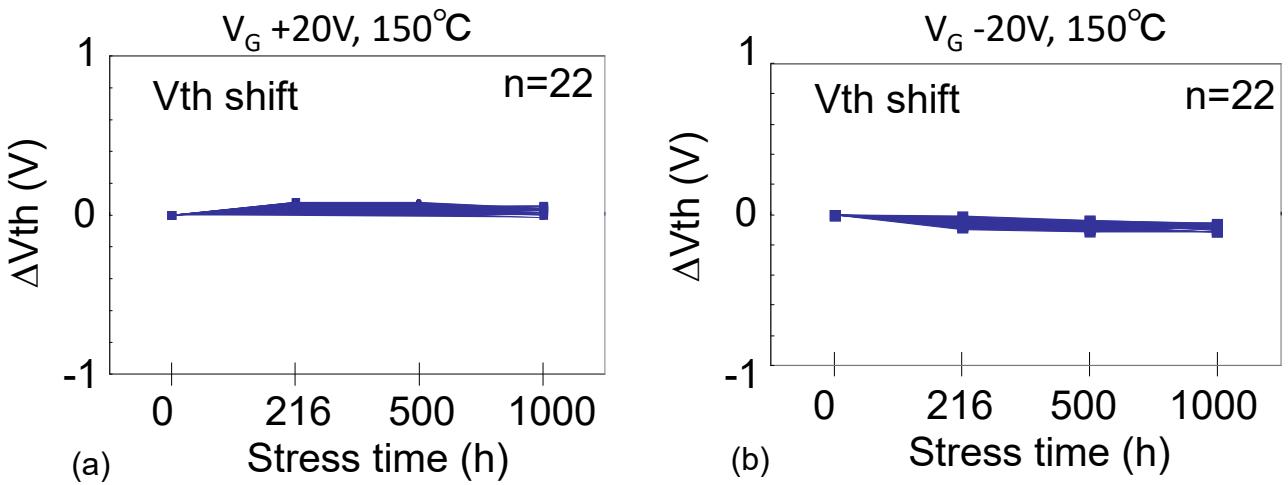

SiC/ $\text{SiO}_2$  界面トラップの MOSFET への影響に関し、三菱電機製のプレーナ型 SiC MOSFET に対し実施したゲートへの電圧ストレス試験(HTGB 試験)の結果を図 1 に示します。試験温度は 150°C とし、ゲートとソースの間に 20V あるいは -20V を印加し続けた場合のしきい値電圧の変化を示しています。いずれの MOSFET もゲート電圧の正、負によらず、しきい値電圧の変動量は小さく、安定性は非常に良好です。あわせて表 1 に 1000 時間のゲート電圧印加後のオン抵抗としきい値電圧の変動量をまとめて示します。しきい値電圧と同様にオン抵抗の変動量も小さく、特に問題になるレベルではありません。

図 1 SiC MOSFET のゲートへの高温( $150^\circ C$ )かつ長時間(1000hr)の電圧印加試験(HTGB 試験)におけるしきい値電圧の経時変化

(a) ゲート電圧が 20V の場合 (b) ゲート電圧が-20V の場合

表 1 SiC MOSFET のゲート電圧印加試験後のオン抵抗としきい値電圧の変化量

| Gate stress condition                    | Electrical characteristics | Deviation |

|------------------------------------------|----------------------------|-----------|

| $V_G = +20V, 150^\circ C$<br>1000h 22pcs | Ron                        | < 3%      |

|                                          | $V_{th}$                   | < 0.1V    |

| $V_G = -20V, 150^\circ C$<br>1000h 22pcs | Ron                        | < 4%      |

|                                          | $V_{th}$                   | < 0.06V   |

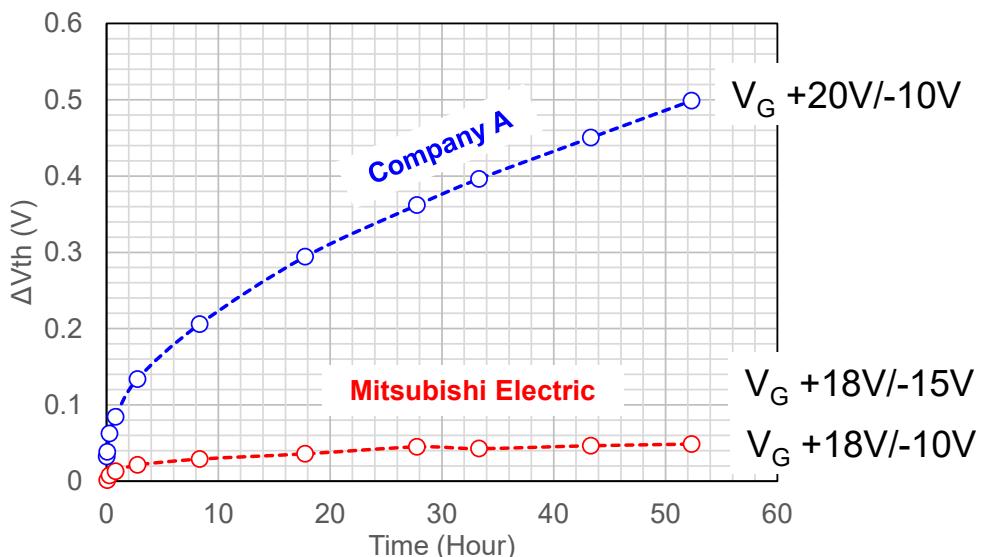

近年、高周波 AC 電圧を SiC MOSFET のゲートに印加した場合のしきい値電圧などの電気特性の経時シフトが関心を集めています。これは SiC/SiO<sub>2</sub> 界面に存在するトラップへの電荷の捕獲や放出が関与する現象であり、電圧の掃引でしばしば見られる特性のヒステリシスとは異なり、時間をかけて徐々に特性がドリフトする現象です。このドリフト量が大きい場合、実用において問題が生じる可能性があるため、アプリケーション側から長期信頼性に対する懸念が示される場合もあります。図 2 に SiC MOSFET のゲートに高周波 AC バイアスを印加した場合のしきい値電圧の経時変化を示します。三菱電機の MOSFET はしきい値電圧のドリフト量は小さく、安定性が良好であり、他社品(Company A)と比較した場合、大きな差が現れています。

図2 SiC MOSFET のゲートに高周波 AC ストレスを印加した場合のしきい値電圧の変化

SiC MOSFETにおいてゲートへのバイアス電圧印加時の電気的特性の不安定な挙動については、これまで様々な報告がなされ、やや混沌とした状況にあり、不安視される場合もあります。MOSFETのゲートが係わる特性の安定性はゲート絶縁膜の作製法やデバイス構造や駆動条件などに強く依存します。加えて、オン抵抗の低減と特性の安定性とは必ずしも両立するものではありません。低抵抗で特性の安定したSiC MOSFETを得るには多くの経験やデータに基づいたプロセスや構造の最適化が必要です。三菱電機のSiC MOSFETのゲート特性については様々なアプリケーションシステムで評価され、安定性が非常に優れていることが示されており、大きな優位性の一つとなっています。

以上

2025年1月