TECHNOLOGY

技術を知る

社会課題の解決と、その先の未来価値創造に向けた最先端のテクノロジーをご紹介します。

ニュースリリース

先端技術総合研究所

三菱電機グループの幅広い事業分野のコア技術・最先端技術の研究開発を行っています。

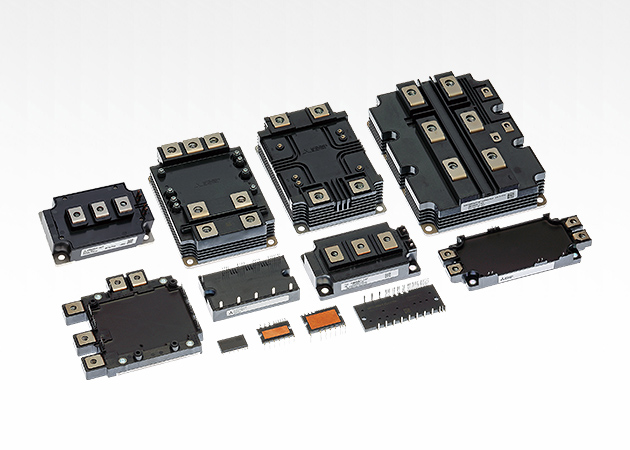

パワーエレクトロニクス、電気、機械、メカトロニクス、環境、材料、エネルギー、デバイス、システムなどの分野において、

新たな時代を切り拓くキー・テクノロジーを提供しています。

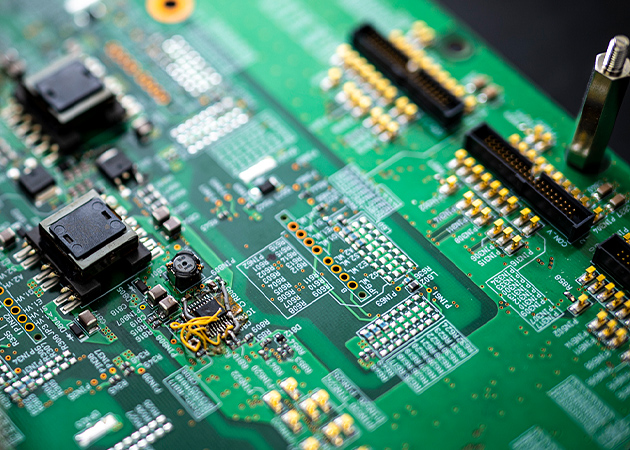

情報技術総合研究所

人工衛星からレーダーシステムやさまざまな分野のセキュリティー技術、AIまで、人・社会に貢献する最先端の技術を生み出しています。

情報、メディアインテリジェンス、光電波・通信技術分野の研究開発と共に、ITを活用した提案型開発も行っています。

統合デザイン研究所

UXデザイン、ソリューションデザイン、プロダクトデザイン、インタラクションデザインなど、ユーザー体験を最優先に考えた技術を駆使し、革新的で使いやすい製品を創造しています。

UXデザイン/ソリューションデザイン/プロダクトデザイン/インタラクションデザイン

先進応用開発センター

自動運転やセンシング技術、制御技術、パワーエレクトロニクス技術に加え、AIやクラウドの応用ノウハウなどを活かした融合技術の開発、ソリューションを創出しています。社内外パートナーとも連携し、より幅広い社会課題の解決に貢献しています。